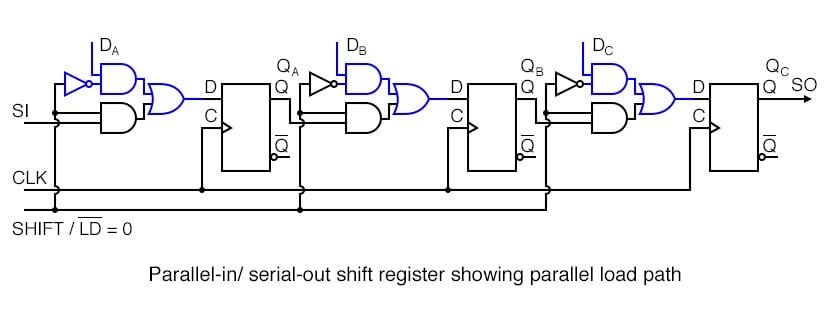

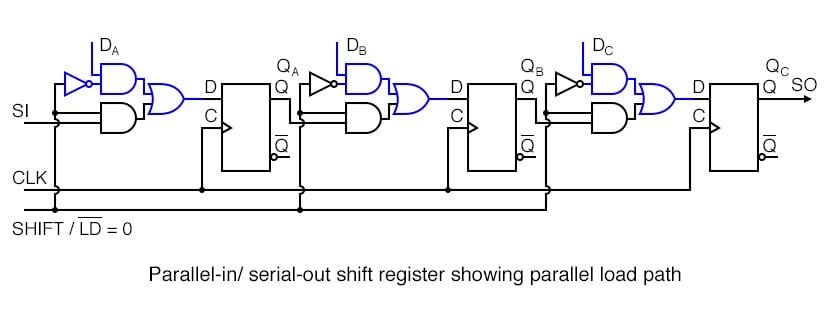

M1 is the parallel input data given to the pin-3 of the first 4×1 MUX to provide parallel mode operation and stores the data into the register. In this mode, the universal shift register shifts the data towards the left. #Parallel to serial converter diagram serial#

Similarly, pin-2 of 4X1 MUX is connected to the serial input for shift-left.In this mode, the register shifts the data towards the right. Pin-1 of the first 4X1 MUX is connected to serial input for shift right.Observe the connections as shown in the figure. Pin-0 of first 4×1 Mux is fed to the output pin of the first flip-flop.It may be shift left operation or shift right operation or parallel mode.

S0 and S1 are the selected pins that are used to select the mode of operation of this register. The design of a 4-bit universal shift register using multiplexers and flip-flops is shown below. If the register operates with a parallel load and shifts the data towards the right and left, then it acts as a universal shift register. In the control state, the information or data in the register would not change even though the clock pulse is applied. CLK pin provides clock pulses to synchronize all the operations. Clear pin clears the register and set to 0. In parallel data transfer, all the parallel inputs and outputs lines are associated with the parallel load. Serial input for shift-left enables the data transfer towards the left and all the serial input and output lines are connected to shift-left mode. The input is given to the AND gate-1 of the flip-flop -1 as shown in the figure via serial input pin. Serial input for shift-right control enables the data transfer towards the right and all the serial input and output lines are connected to the shift-right mode. Hence, Universal shift registers can perform input/output operations with both serial and parallel loads.Ĥ-bit Universal shift register diagram is shown below. Shift right operation – stores the data and transfers the data by shifting towards right in the serial path. Shift left operation – stores the data and transfers the data shifting towards left in the serial path. Parallel load operation – stores the data in parallel as well as the data in parallel. Universal shift registers are capable of performing 3 operations as listed below. It is also known as a parallel-in-parallel-out shift register or shift register with the parallel load.

S0 and S1 are the selected pins that are used to select the mode of operation of this register. The design of a 4-bit universal shift register using multiplexers and flip-flops is shown below. If the register operates with a parallel load and shifts the data towards the right and left, then it acts as a universal shift register. In the control state, the information or data in the register would not change even though the clock pulse is applied. CLK pin provides clock pulses to synchronize all the operations. Clear pin clears the register and set to 0. In parallel data transfer, all the parallel inputs and outputs lines are associated with the parallel load. Serial input for shift-left enables the data transfer towards the left and all the serial input and output lines are connected to shift-left mode. The input is given to the AND gate-1 of the flip-flop -1 as shown in the figure via serial input pin. Serial input for shift-right control enables the data transfer towards the right and all the serial input and output lines are connected to the shift-right mode. Hence, Universal shift registers can perform input/output operations with both serial and parallel loads.Ĥ-bit Universal shift register diagram is shown below. Shift right operation – stores the data and transfers the data by shifting towards right in the serial path. Shift left operation – stores the data and transfers the data shifting towards left in the serial path. Parallel load operation – stores the data in parallel as well as the data in parallel. Universal shift registers are capable of performing 3 operations as listed below. It is also known as a parallel-in-parallel-out shift register or shift register with the parallel load.

Unidirectional shift registers and bidirectional shift registers are combined together to get the design of the universal shift register. It can be used to perform input/output operations in both serial and parallel modes. Definition: A register that can store the data and /shifts the data towards the right and left along with the parallel load capability is known as a universal shift register.

0 kommentar(er)

0 kommentar(er)